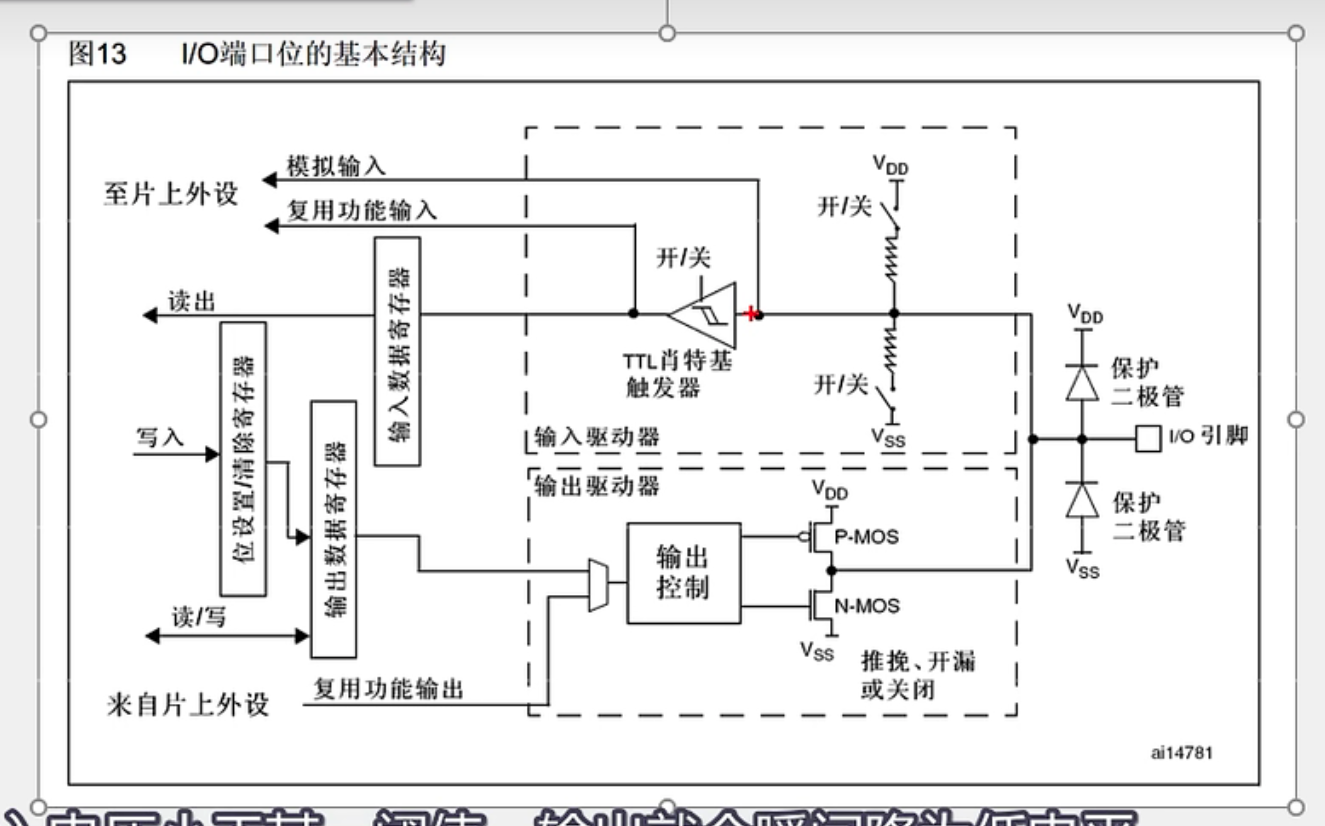

最右边为引脚。

两个保护二极管,VDD 接 3.3V,VSS 接 0V。如果流入的电压大于 3.3V,会击穿 VDD 处的二极管,电流会顺着流出,不会流入电路中。如果流入的电压小于 0V(负电压),电流会从 VSS 流出,不会流入电路中。

右上方,上拉电阻和下拉电阻。若接了引脚,则电平由引脚端控制;未接引脚时,由上拉电阻、下拉电阻进行控制,否则电路状态为悬空状态,容易发生改变。上拉电阻保证引脚高电平,下拉电阻保证引脚低电平(默认高低电平)。

- 施密特触发器:用于整流(整形),如果电压高于阈值,输出高电平;低于阈值,输出低电平。

- 输出控制:

- 推挽输出(强推输出):P-MOS 和 N-MOS 均有效。数据寄存器为 1 时,上通下断,引脚接 VDD,输出高电平。数据寄存器为 0 时,下通上断,引脚接 VSS,输出低电平。

- 开漏输出:P-MOS 无效。数据寄存器为 1 时,下断开,输出高阻;数据寄存器为 0 时,下通路,输出低电平。